# MSI-P415 ANALOG INPUT CARD USER MANUAL

# PC/104 Embedded Industrial Analog I/O Series

# Microcomputer Systems, Inc.

1814 Ryder Drive "Baton Rouge, LA 70808 Ph (225) 769-2154 "Fax (225) 769-2155 Email: staff@microcomputersystems.com http://www.microcomputersystems.com

# **CONTENTS**

| I. INTRODUCTION                 | 3  |

|---------------------------------|----|

| II. HARDWARE DESCRIPTION        | 5  |

| A. Card Configuration           |    |

| B. Card Addressing              |    |

| C. Interrupt Connections        |    |

| D. Connecting Inputs to J1      |    |

| IIII. PROGRAMMING               | 9  |

| A. Control Register Format      |    |

| B. Performing a Conversion      |    |

| C. Reading the Data Register    |    |

| D. Input Data Formats           |    |

| E. Power-Down Modes             |    |

| F. Example BASIC Program        |    |

| G. Example 'C' Program Sequence |    |

| IV. SPECIFICATIONS              | 15 |

| APPENDIX                        | 15 |

| Circuit Diagrams                |    |

| MSI_D415                        | 15 |

#### I. INTRODUCTION

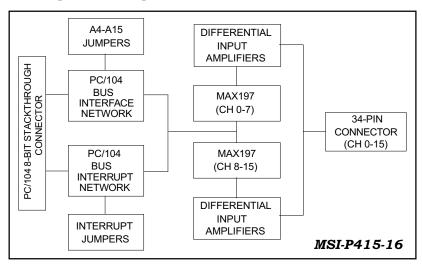

The MSI-P415 is a low cost, high performance 12-bit differential input analog card designed for use with all PC/104 embedded systems. Two models provide input capacities of 8 or 16 channels which operate from a single +5V supply. Software programmable input ranges are 0-5V, 0-10V,  $\pm$ 5V and  $\pm$ 10V with a linearity of 1/2 LSB and input impedance of 1M $\Omega$ . In addition, a fault condition on any channel will not effect the conversion result on the selected channel. A block diagram of the card is shown below.

The card employs up to two MAX197 eight-channel A/D converters that incorporate a precision 2.5V reference source with buffer amp, an internal 1.56 MHz clock, and successive approximation and internal input track/hold circuitry to convert the analog signal of each channel into a 12-bit digital signal. Low span and offset errors result in no adjustments being required for these functions. Typical total conversion times of 12 us gives a sample rate of 83 ksps for each group of eight channels yielding rates up to 166 ksps for 16 input channels.

Figure 1. Block Diagram of the MSI-P415-16.

The card is I/O mapped using 16-bit addressing to select the input channels and device status. Option jumpers are provided by JP1 for specifying the card address (A4 - A15) and interrupt processing is provided for IRQ4 thru IRQ7 and IRQ9 using options jumpers, as described in the next section.

#### II. HARDWARE DESCRIPTION

# A. Card Configuration

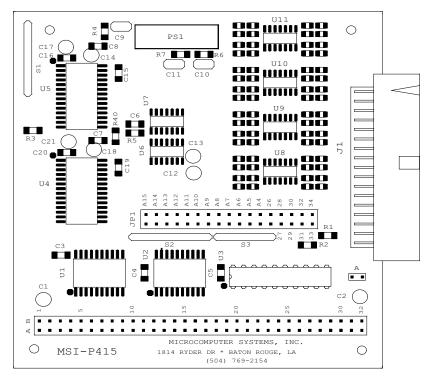

The MSI-C415 card is a CMOS design using through-hole and surface-mounted devices. The card configuration is shown in Figure 2 and a circuit diagram of the network is given in the Appendix. The input signals for channels 0 thru 15 are applied to connector J1. These signals are directed to the input terminals of A/D converters U6 (Channels 0-7) and U7 (Channels 8-15).

Jumper block JP1 is used for address selection (Pins 1 thru 24) and interrupt configuration (Pins 25 thru 34), as described below.

Figure 2. MSI-P415 card outline.

# **B.** Card Addressing

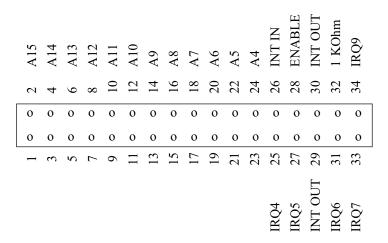

The card address is set by installing appropriate jumpers on JP1, pins 1 thru 24, as shown in Fig. 3. An <u>uninstalled</u> jumper for a given address bit sets the bit to 1 (true) and an <u>installed</u> jumper sets the bit equal to 0 (false). Addresses A4 thru A15 are jumper selectable for defining the *base* address of the card from 0000H to FFF0H on integral 10H boundaries, where H denotes a hexadecimal number. To assign a base address of 3040H, for example, install jumpers JP1-A4, JP1-A5, JP1-A7 thru JP1-A11, JP1-A14 and JP1-A15. Pins 25 thru 34 are used to configure the interrupt connections, if interrupts are used, as described in the Section II.C.

The MAX197 converters each have two registers for performing data conversions, a control output register (C) and a input data register (I). A third register implemented on the card for denoting interrupt status is called the status register. The addresses of the control, input data (C/I) and status for each channel is given in Table 1. The functions of the control, the input data (hi and lo bytes), and status registers are described in the Section III.

Figure 3. Jumper block JP1 configuration.

Table 1. Analog Converter Control Register Addresses

| Channels | Control Output (C) | Data Input (I)             | Status / Bit |

|----------|--------------------|----------------------------|--------------|

| 0-7      | base+0             | base+0 (lo)<br>base+1 (hi) | base+8 / 0   |

| 8-15     | base+2             | base+2 (lo)<br>base+3 (hi) | base+8 / 1   |

# C. Interrupt Connections

Interrupt connections are implemented by pins 25 thru 34 of JP1. The steps in the procedure are as follows.

- 1) Pin 30 (INT OUT) is the composite interrupt signal from the analog converters (see circuit diagram in Appendix). This is jumpered to a single desired interrupt, IRQ4 thru IRQ9, of JP1 shown in Fig. 3. This connection causes the interrupt selected to be activated when a conversion is performed.

- 2) If no other cards in the system are using the interrupt line chosen in step 1, proceed to step 3.

Pin 26 of JP1 (INT IN) is used to control the tri-state buffer of INT OUT when other cards are using the same interrupt line chosen in step 1. In this case, connect pins 26 and 28 of JP1. This results in the tri-state buffer of INT OUT being enabled only when an interrupt request is active. The status is then checked to determine which interrupt is active, as described in Section III.

3) Pin 32 of JP1 (1 KOhm pull-down resistor) is used to properly terminate the interrupt line selected in step 1. This pin should be jumpered to the interrupt line on only one card in the system.

# D. Connecting Inputs to J1.

Inputs are interconnected to the card via J1 using 16-pin or 34-pin flat cable connectors for 8-channel and

16-channel models, respectively. Pin assignments are

Table 2a. Connector J1 Pin assignments for MSI-P415-8.

| Input | nput Pin |       | Pin  |

|-------|----------|-------|------|

| Ch 0+ | J1-16    | Ch 4+ | J1-8 |

| Ch 0- | J1-15    | Ch 4  | J1-7 |

| Ch 1+ | J1-14    | Ch 5+ | J1-6 |

| Ch 1- | J1-13    | Ch 5- | J1-5 |

| Ch 2+ | J1-12    | Ch 6+ | J1-4 |

| Ch 2- | J1-11    | Ch 5- | J1-3 |

| Ch 3+ | J1-10    | Ch 7+ | J1-2 |

| Ch 3- | J1-9     | Ch 7- | J1-1 |

Table 2b. Connector J1 Pin assignments for MSI-P415-16.

| Input          | Pin            | Input          | Pin          | Input            | Pin | Input            | Pin |

|----------------|----------------|----------------|--------------|------------------|-----|------------------|-----|

| Ch 0+<br>Ch 0- | J1-16<br>J1-15 | _              | J1-8<br>J1-7 | Ch 8+<br>Ch 8-   |     | Ch 12+<br>Ch 12- |     |

| Ch 1+<br>Ch 1- | J1-14<br>J1-13 | Ch 5+<br>Ch 5- | J1-6<br>J1-5 | Ch 9+<br>Ch 9-   |     | Ch 13+<br>Ch 13- |     |

| Ch 2+<br>Ch 2- | J1-12<br>J1-11 | Ch 6+<br>Ch 6- | J1-4<br>J1-3 | Ch 10+<br>Ch 10- |     | Ch 14+<br>Ch 14- |     |

| Ch 3+<br>Ch 3- | J1-10<br>J1-9  | Ch 7+<br>Ch 7- | J1-2<br>J1-1 | Ch 11+<br>Ch 11- |     | Ch 15+<br>Ch 15- |     |

Note: Pin P1-33 is card common and P1-34 is connected to +5V using Jumper A.

#### III. PROGRAMMING

Performing data conversions involves a write operation to the control register of the appropriate MAX197, which selects the mux channel and configures the input mode. The data is then read, lo byte and hi byte, when the conversion has been completed.

# A. Control Register Format

The control register is an 8-bit (write-only) register that selects the mux channel and mode of the converter. The format is

| D7(MSB) | D6  | D5     | D4  | D3  | D2 | D1 | D0(LSB) |

|---------|-----|--------|-----|-----|----|----|---------|

| PD1     | PD0 | ACQMOD | RNG | BIP | A2 | A1 | A0      |

#### where

PD1, PD0 select the clock and power down mode (Table 3).

ACQMOD - 0 = internally controlled acquisition,

1 = externally controlled acquisition.

RNG selects the full-scale voltage range (Table 4).

BIP selects unipolar or bipolar conversion mode (Table 4).

A2, A1, A0 select the desired input channel 0-7 of the MAX197.

Table 3. Clock and Power Down Selection

| PD1 | PD0 | DEVICE MODE                                   |  |  |

|-----|-----|-----------------------------------------------|--|--|

| 0   | 0   | Normal Operation/External Clock Mode          |  |  |

| 0   | 1   | Normal Operation/Internal Clock Mode          |  |  |

| 1   | 0   | Standby Power-down (STBYPD); clock unaffected |  |  |

| 1   | 1   | Full Power-down (FULLPD); clock unaffected    |  |  |

Table 4. Range and Polarity Selection

|     | _   |                 |

|-----|-----|-----------------|

| BIP | RNG | INPUT RANGE (V) |

| 0   | 0   | 0 to 5          |

| 0   | 1   | 0 to 10         |

| 1   | 0   | ±5              |

| 1   | 1   | ±10             |

|     |     | -               |

The card is designed to operate using the internal clock with PD1=0 and PD0=1 in normal operation. The internally controlled acquisition (ACQMOD = 0) is normally used .

# B. Performing a Conversion

Conversions are initiated with a write operation to the control register (Table 1), which selects the mux channel of the desired MAX197 (U5, Channel 0-7 or U4, Channel 8-15) and configures the device mode. Selecting ACQMOD = 0 in the control register selects the internal acquisition mode. This causes the write to the control register to initiate the acquisition interval whose duration is internally timed. Conversion starts when this six-clock-cycle acquisition interval ends. Writing a new control byte during the conversion cycle will abort the conversion and start a new acquisition interval.

# C. Reading the Data Register

Conversions are complete when the appropriate status bit (Table 1) becomes 0 following a write to the control register. Channels 0-7 (U5), for example, are ready when bit 0 at address *base*+8 is 0. The data can now be read at the appropriate lo and hi byte addresses for the lo and hi bytes of the channel selected (A2, A1, A0 of the control register). In the case of channels 0-7, addresses *base*+0 and *base*+1, respectively, are read.

# D. Input Data Format

Unipolar Mode - the output data format is binary. In this case, 0 volts input yields 000H, where H denotes a hexadecimal number. The value increases linearly from 000H to FFFH with increasing input voltage. A +FS input (full-scale +5V or +10V ranges) gives FFFH.

Bipolar Mode - the output data format is twos-complement binary. In this case, a -FS input ( $\pm 5V$  or  $\pm 10V$  ranges) yields 800H. The value increases linearly from 800H toward FFFH as the input voltage changes from -FS toward 0 volts.

At 0 volts input (in the ideal case), the value is 000H. Again, the value increases linearly from 000H toward 7FFH as the input voltage changes from 0 toward +FS volts.

The lo byte read, bits D0 thru D7, of the input data is the low byte B0 thru B7 of the conversion result. The hi byte read of the input data contains bits B8 thru B11 of the conversion result in bits D0 thru D3. Bits D4 thru D7 contain all 0's and all 1's, respectively, for the unipolar and bipolar modes.

#### E. Power-Down Modes

To save power, the converters can be placed into a low-power shutdown mode between conversions. Two programmable power-down modes are available. Select STDBYPD or FULLPD by programming PD0 and PD1 in the control register. When software power-down is asserted, it becomes effective only after the end of conversion. In both power-down modes, the interface remains active and conversion results may be read. Input overvoltage protection is active. The converter returns to normal operation on the first write to the control register. In STDBYPD each device typically consumes 700uA and in FULLPD 120 uA maximum.

The converter voltage reference remains active in STDBYPD. This is a DC power state that does not degrade after power-down of any duration and any sampling rate can be used without regard to start-up delays. In FULLPD, however, start-up delays will effect the conversion. It is recommended when using this mode that a STDBYPD power-down cycle be performed prior to starting conversions to allow the reference voltage to stabilize.

Selecting STDBYPD on every conversion automatically shuts the MAX197 down after each conversion without requiring any start-up time on the next conversion.

# F. Example BASIC Program

A simple BASIC program that inputs continually inputs channels 0 thru 7 for the 5V unipolar mode and lists the results to the console is given below.

```

10 BASEADDR=&H300 'insert jumpers A4 thru A7, A10 thru A15

20 CBYTE = &H40 'Control Byte for 5V Unipolar Mode

30 FOR I = 0 TO 7

40 OUT BASEADDR,CBYTE+I 'Write Control Byte

50 WHILE (INP(BASEADDR+8) AND 1)=1:WEND 'Test Status

60 X=INP(BASEADDR) 'Read LO Byte

70 Y=INP(BASEADDR+1) 'Read HI Byte

80 X=X+256*(Y AND &HF) 'Mask off 4 MSB's of HI Byte

90 'Print CH0-CH4, Linefeed, CH4-CH7

100 IF I=3 OR I=7 THEN PRINT HEX$(X) ELSE PRINT HEX$(X),

110 NEXT

120 PRINT" "

130 GOTO 30 'Go Again

```

# G. Example 'C' Program Sequence

For a simple 'C' program illustration using software polling of the device status, consider a case with the following parameters and events.

- 1) A base address for the card of 7FF0H (insert jumper A15).

- 2) Read A/D channel 3 (input to U5) in the +5V unipolar mode and store the result in CH\_3\_INPUT.

- 3) Read A/D channel 9 (input to U4) in the ±10V bipolar mode and store the result in CH\_9\_INPUT.

A simple program sequence for this operation is

#### /\* Constant declarations \*/

```

/* card base address */

#define base address

0x7ff0

#define control byte 5

0x40

/* control byte for +5V range */

#define control byte 5B

0x48

/* control byte for ±5V range */

#define control byte 10

/* control byte for +10V range */

0x50

/* control byte for ±10V range */

#define control byte 10B 0x58

#define delay count

1000

/* delay count for converter

time-out */

```

```

/* Memory assignments */

int A D value, CH 3 INPUT, CH 9 INPUT;

/* Routine to input A/D channel CHAN(0-15) for control byte C BYTE and

returns 0 on a converter time-out error. Stores converted value in

A D value */

int input A D(int CHAN, int C BYTE)

{

int converter error, a, i, ch group;

if( 0 \le CHAN & CHAN < 8 ) ch group =0;

else if( 7 < CHAN && CHAN < 16 )

{ch group = 2; CHAN = CHAN - 8;}

outp( base address+ch group, C BYTE + CHAN ); //write control byte

if( ch group < 1 ) a = 1; //Ch 0-7

else a = 2; //Ch 8-15

i=0:

do ++i;

while ( (inp(base address + 8) & a) && i < delay count );

if( i == delay count ) converter error = 1;/* converter time-out error */

else converter error = 0;

A D value = inp( base address + ch group ); /* get converter value */

A D value = A D value + ((inp(base address + ch group + 1) &

0xf) << 8);

return( converter error );

}

void main(void)

{

/* Input channel 3 for +5V range and store if no time out error */

if(!input A D(3, control byte 5)) CH 3 INPUT = A D value;;

/* Input channel 9 for ±10V range and store if no time out error */

if(!input A D(9, control byte 10B)) CH 9 INPUT = A D value;;

```

}

The function *input\_A\_D*( *int CHAN*, *int C\_BYTE* ) above is written in general terms to permit calls from the main routine or from other user defined functions by simply using the appropriate CHAN and C\_BYTE values for the input channel desired and the desired input range.

#### IV. SPECIFICATIONS

PC/104 8-bit, stackthrough

Analog Inputs

Channels 8 to 16 in groups of 8

Converter MAXIM MAX197

Differential

Input Ranges 0-5V, 0-10V, ±5V, ±10V

Resolution 12 bits

Conversion Rate 82 ksps per 8 channels

Non-linearity ±1/2 LSB

Offset Error < 0.5% of Span

Gain Error < 0.5% of Span

Signal-to-Noise 70 dB min

Input Resistance 1 M $\Omega$

Internal Reference

Ref Out Voltage 4.096 V ±1.5% max.

Temp. Coeff. 40 ppm/°C

Connectors

MSI-P414-8 One (1) 3M 30316-5002 or eq. (16-pin) MSI-P414-16 One (1) 3M 30334-5002 or eq. (34-pin)

Interrupts

Channels One, sharing with tri-state

buffer for IRQ4-7, 9

**Option Jumpers** .025" square posts, 0.1" grid

Electrical & Environmental +5V @ 70 mA typical

-40° to 85°C

# **APPENDIX**

# **Circuit Diagrams**

**MSI-P415**